# MOS INTEGRATED CIRCUIT $\mu$ PD17104

### **4 BIT SINGLE-CHIP MICROCONTROLLER**

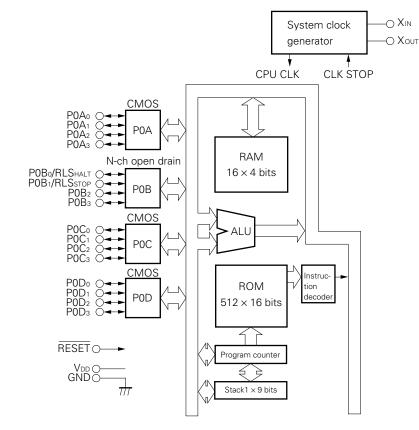

The  $\mu$ PD17104, tiny microcontroller, consists of 1K-byte (512 × 16) ROM, 16 × 4 bit RAM, and 16 input/output ports.

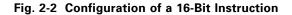

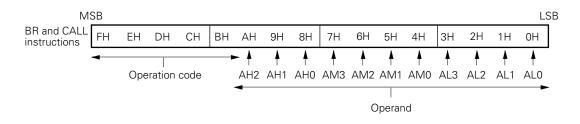

The 17K architecture of the CPU uses general registers so that data memory can be manipulated directly for effective programming. Every instruction is 1 word long, consisting of 16 bits.

#### **FEATURES**

- Program memory (ROM) : 1K bytes (512 × 16 bits)

- Data memory (RAM) : 16 × 4 bits

- Input/output ports : 16 ports (including four N-ch open-drain outputs)

- Instruction execution time : 2  $\mu$ s (when operating at 8 MHz)

- Number of instructions : 24 (Each instruction is 1 word long.)

- Stack level : 1

- A standby function (with the STOP and HALT instructions)

- Data memory can retain data on low voltage (2.0 V at minimum).

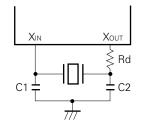

- An oscillator for the system clock (for ceramic resonator)

- Operating supply voltage : 2.7 to 6.0 V (at 2 MHz)

4.5 to 6.0 V (at 8 MHz)

#### **APPLICATIONS**

• Controlling electric appliances or toys

#### **ORDERING INFORMATION**

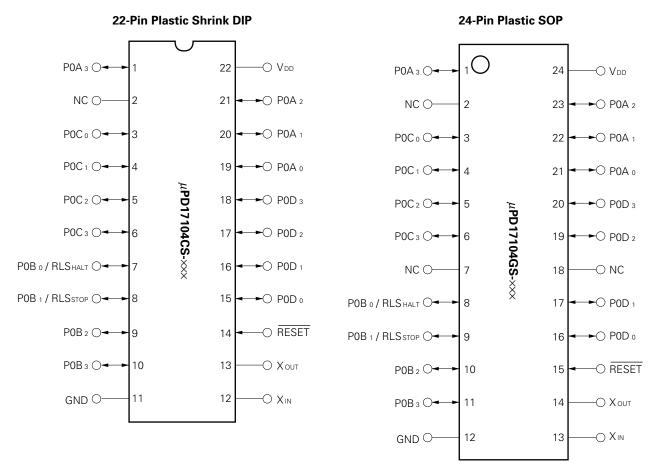

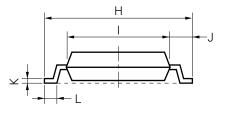

| Part number                        | Package                             | Quality grade |

|------------------------------------|-------------------------------------|---------------|

| μPD17104CS-×××                     | 22-pin plastic shrink DIP (300 mil) | Standard      |

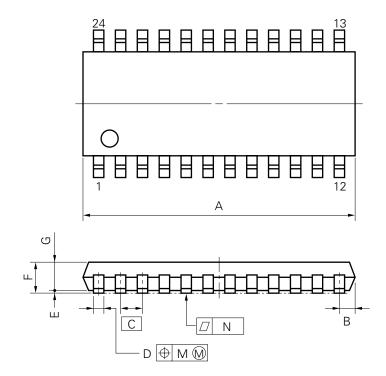

| $\mu$ PD17104GS- $\times$ $\times$ | 24-pin plastic SOP (300 mil)        | Standard      |

Please refer to *Quality Grades on NEC Semiconductor Devices* (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on devices and its recommended applications.

The information in this document is subject to change without notice.

#### **PIN CONFIGURATION (TOP VIEW)**

**BLOCK DIAGRAM OF THE \muPD17104**

#### PINS

#### Pin functions

#### • Port pins

| Pin                                        | I/O | Function                                                                                                                                                                                                                                                                           | Reset                       |

|--------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| P0A0-P0A3                                  | I/O | CMOS (push-pull) 4-bit I/O port (port 0A)                                                                                                                                                                                                                                          | High impedance (input mode) |

| P0B0/RLSHALT<br>P0B1/RLSSTOP<br>P0B2, P0B3 | I/O | <ul> <li>For releasing the HALT mode</li> <li>For releasing the STOP mode</li> <li>N-ch open-drain 4-bit I/O port (port 0B)</li> <li>A built-in pull-up resistor can be connected with mask option bit by bit.</li> <li>This open-drain port has a withstand voltage of</li> </ul> | High Level (input mode)     |

| P0C₀-P0C₃                                  | I/O | CMOS (push-pull) 4-bit I/O port (port 0C)                                                                                                                                                                                                                                          | High impedance (input mode) |

| P0D0-P0D3                                  | I/O | CMOS (push-pull) 4-bit I/O port (port 0D)                                                                                                                                                                                                                                          | High impedance (input mode) |

#### • Non-port pins

| Pin       | I/O   | Function                                                                                                             |

|-----------|-------|----------------------------------------------------------------------------------------------------------------------|

| RESET     | Input | <ul> <li>System reset input pin</li> <li>A built-in pull-up resistor can be connected with a mask option.</li> </ul> |

| Vdd       | -     | Positive power supply pin                                                                                            |

| GND       | -     | GND pin                                                                                                              |

| Xin, Xout | -     | Pins to be connected to the system clock resonator                                                                   |

I/O: Input/output

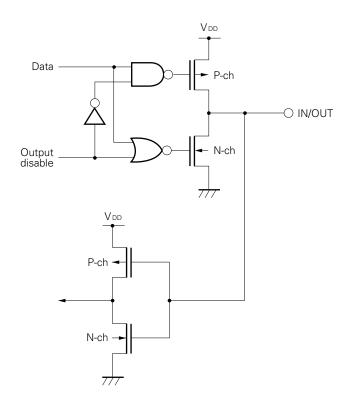

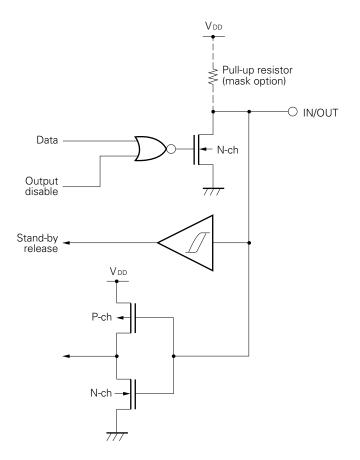

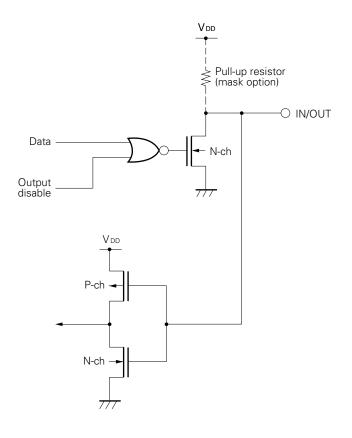

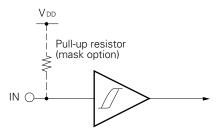

#### Equivalent input/output circuits

Below are simplified diagrams of the equivalent input/output circuits.

#### (1) P0A, P0C, and P0D

(2) P0B<sub>0</sub> and P0B<sub>1</sub>

#### (3) P0B2 and P0B3

(4) RESET

#### \* HANDLING UNUSED PINS

Connect unused pins as follows:

| Pin  |                                            | Din                | Conditions and handling                                                                   |                                                                           |  |

|------|--------------------------------------------|--------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

|      |                                            |                    | Internal                                                                                  | External                                                                  |  |

| Port | Input                                      | P0A, P0C, P0D      | -                                                                                         | Connect to $V_{_{DD}}$ through pull-up resis-                             |  |

|      | modeP0BOutputP0A, P0C, P0Dmode(CMOS ports) |                    | Pull-up resistors that can be specified by the mask option are not incorporated.          | tors. Or, connect to ground through pull-down resistors <sup>Note</sup> . |  |

|      |                                            |                    | Pull-up resistors that can be specified with the mask option are incorporated.            | Leave open.                                                               |  |

|      |                                            |                    | -                                                                                         |                                                                           |  |

|      |                                            | P0B<br>(N-ch open- | Outputs low level without pull-up resistors<br>that can be specified with the mask option |                                                                           |  |

|      |                                            |                    | Outputs high level with pull-up resistors that can be specified with the mask option      |                                                                           |  |

**Note** When a pin is pulled up to V<sub>DD</sub> or pulled down to ground outside the chip, take the driving capacity and maximum current consumption of a port into consideration. When using high-resistance pull-up or pull-down resistors, apply appropriate countermeasures to ensure that noise is not attracted by the resistors. Although the optimum pull-up or pull-down resistor varies with the application circuit, in general a resistor of 10 to 100 kilohms is suitable.

# Caution To fix the output level of a pin, it is recommended that the level be specified repeatedly within a loop in a program.

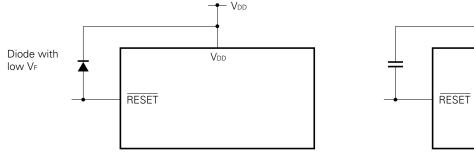

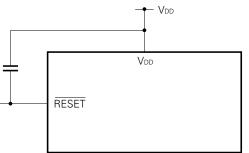

#### NOTES ON USE OF THE RESET PIN

The  $\overline{\text{RESET}}$  pin has the test mode selecting function for testing the internal operation of the  $\mu$ PD17104 (IC test), besides the functions shown in **PINS**.

Applying a voltage exceeding V<sub>DD</sub> to the RESET pin causes the  $\mu$ PD17104 to enter the test mode. When noise exceeding V<sub>DD</sub> comes in during normal operation, the device is switched to the test mode.

For example, if the wiring from the  $\overline{\text{RESET}}$  pin is too long, noise may be induced on the wiring, causing this mode switching.

When installing the wiring, lay the wiring in such a way that noise is suppressed as much as possible. If noise yet arises, use an external part to suppress it as shown below.

Connect a diode with low VF between the pin

Connect a capacitor between the pin and VDD.

and VDD.

#### CONTENTS

| 1. | PROG  | OUNTER (PC) | 9                                                              |    |

|----|-------|-------------|----------------------------------------------------------------|----|

|    | 1.1   | CONFIG      | GURATION OF THE PROGRAM COUNTER (PC)                           | 9  |

|    | 1.2   | FUNCT       | ONS OF THE PROGRAM COUNTER (PC)                                | 9  |

|    |       |             |                                                                |    |

| 2. | STAC  | к           |                                                                | 10 |

| 3. | PROG  | RAM M       | IEMORY (ROM)                                                   | 11 |

| 0. | mot   |             |                                                                | •• |

| 4. | DATA  | мемо        | RY (RAM)                                                       | 12 |

|    | 4.1   | CONFIG      | GURATION OF THE DATA MEMORY (RAM)                              | 12 |

|    |       | 4.1.1       | Functions of the General Data Memory                           | 12 |

|    |       | 4.1.2       | Functions of the General Register                              | 12 |

|    |       | 4.1.3       | Functions of the Port Register                                 | 12 |

|    |       | 4.1.4       | Functions of the System Register                               | 13 |

|    |       |             |                                                                |    |

| 5. | ALU I | BLOCK .     |                                                                | 16 |

|    | 5.1   | ALU BL      | OCK CONFIGURATION                                              | 16 |

|    | 5.2   | FUNCT       | IONS OF THE ALU BLOCK                                          | 16 |

|    |       | 5.2.1       | Functions of the ALU                                           | 16 |

|    |       | 5.2.2       | Functions of Temporary Registers A and B                       | 20 |

|    |       | 5.2.3       | Functions of the Status Flip-Flop                              | 20 |

|    |       | 5.2.4       | Performing Operations in 4-Bit Binary                          | 21 |

|    |       | 5.2.5       | Performing Operations in BCD                                   | 21 |

|    |       | 5.2.6       | Performing Operations in the ALU Block                         | 22 |

|    | 5.3   | ARITHM      | IETIC OPERATIONS (ADDITION AND SUBTRACTION IN 4-BIT BINARY AND |    |

|    |       | BCD)        |                                                                | 23 |

|    |       | 5.3.1       | Addition and Subtraction When CMP = 0 and BCD = 0              | 23 |

|    |       | 5.3.2       | Addition and Subtraction When CMP = 1 and BCD = 0              | 23 |

|    |       | 5.3.3       | Addition and Subtraction When CMP = 0 and BCD = 1              | 24 |

|    |       | 5.3.4       | Addition and Subtraction When CMP = 1 and BCD = 1              | 24 |

|    |       | 5.3.5       | Warnings Concerning Use of Arithmetic Operations               | 25 |

|    | 5.4   | LOGICA      | L OPERATIONS                                                   | 25 |

|    | 5.5   | BIT EVA     | ALUATIONS                                                      | 26 |

|    |       | 5.5.1       | TRUE (1) Bit Evaluation                                        | 26 |

|    |       | 5.5.2       | FALSE (0) Bit Evaluation                                       | 27 |

|    | 5.6   | СОМРА       | RISON EVALUATIONS                                              | 27 |

|    |       | 5.6.1       | "Equal" Evaluation                                             | 28 |

|    |       | 5.6.2       | "Not Equal" Evaluation                                         | 28 |

|    |       | 5.6.3       | "Greater Than or Equal" Evaluation                             | 29 |

|    |       | 5.6.4       | "Less Than" Evaluation                                         | 29 |

|    | 5.7   | ROTAT       | IONS                                                           | 30 |

|    |       | 5.7.1       | Rotation to the Right                                          | 30 |

|    |       | 5.7.2       | Rotation to the Left                                           | 31 |

$\star$

# NEC

|   | 6.  | 6. PORTS |                                                  |    |  |  |  |  |

|---|-----|----------|--------------------------------------------------|----|--|--|--|--|

|   |     | 6.1      | PORT 0A (P0A₀ TO P0A₃)                           | 32 |  |  |  |  |

|   |     | 6.2      | PORT 0B (P0B0/RLSHALT, P0B1/RLSSTOP, P0B2, P0B3) | 32 |  |  |  |  |

|   |     | 6.3      | PORT 0C (P0C <sub>0</sub> TO P0C <sub>3</sub> )  | 32 |  |  |  |  |

|   |     | 6.4      | PORT 0D (P0D0 TO P0D3)                           | 33 |  |  |  |  |

| * |     | 6.5      | Notes on Manipulating Port Registers             | 34 |  |  |  |  |

|   | 7.  | STAP     | NDBY FUNCTIONS                                   | 35 |  |  |  |  |

|   |     | 7.1      | HALT MODE                                        | 35 |  |  |  |  |

|   |     | 7.2      | STOP MODE                                        | 35 |  |  |  |  |

|   |     | 7.3      | SETTING AND RELEASING THE STANDBY MODES          | 35 |  |  |  |  |

| * |     | 7.4      | HARDWARE STATUSES IN STANDBY MODE                | 36 |  |  |  |  |

|   |     | 7.5      | TIMING FOR RELEASING THE STANDBY MODES           | 36 |  |  |  |  |

|   | 8.  | RESE     | T FUNCTION                                       | 38 |  |  |  |  |

|   |     | 8.1      | SYSTEM RESET                                     | 38 |  |  |  |  |

|   | 9.  | RESE     | RVED WORDS USED IN ASSEMBLY LANGUAGE             | 39 |  |  |  |  |

|   |     | 9.1      | MASK-OPTION PSEUDO INSTRUCTIONS                  | 39 |  |  |  |  |

|   |     |          | 9.1.1 OPTION and ENDOP Pseudo Instructions       | 39 |  |  |  |  |

|   |     |          | 9.1.2 Mask-Option Definition Pseudo Instructions | 39 |  |  |  |  |

|   |     | 9.2      | RESERVED SYMBOLS                                 | 41 |  |  |  |  |

|   | 10. | INST     | RUCTION SET                                      | 42 |  |  |  |  |

|   |     | 10.1     | INSTRUCTION SET LIST                             | 42 |  |  |  |  |

|   |     | 10.2     | INSTRUCTIONS                                     | 43 |  |  |  |  |

| * |     | 10.3     | ASSEMBLER (AS17K) BUILT-IN MACRO INSTRUCTIONS    | 45 |  |  |  |  |

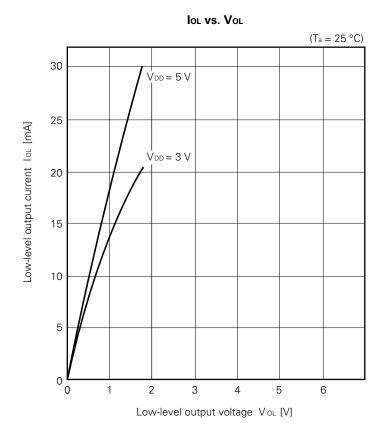

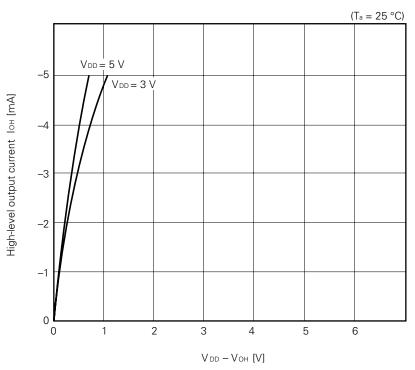

|   | 11. | ELEC     | TRICAL CHARACTERISTICS                           | 46 |  |  |  |  |

|   | 12. | CHA      | RACTERISTIC CURVES (REFERENCE)                   | 50 |  |  |  |  |

|   | 13. | PAC      | AGE DRAWINGS                                     | 52 |  |  |  |  |

|   | 14. | RECO     | OMMENDED SOLDERING CONDITIONS                    | 56 |  |  |  |  |

|   | 15. | ΤΙΝΥ     | MICROCONTROLLER FAMILY                           | 57 |  |  |  |  |

|   | AP  | PENDI    | X DEVELOPMENT TOOLS                              | 58 |  |  |  |  |

#### 1. PROGRAM COUNTER (PC)

#### 1.1 CONFIGURATION OF THE PROGRAM COUNTER (PC)

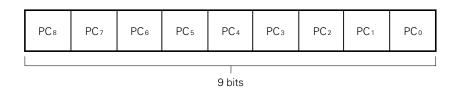

As shown in Fig. 1-1, the program counter is a 9-bit binary counter.

#### Fig. 1-1 Program Counter

#### 1.2 FUNCTIONS OF THE PROGRAM COUNTER (PC)

The program counter specifies the address of a program memory (ROM) or a program.

Usually, every time an instruction is executed, the program counter is incremented by one. When a branch instruction (BR), a subroutine call instruction (CALL), or a return instruction (RET) is executed, the address specified in the operand is loaded in the PC. Then the instruction in the address is executed. When a skip instruction is executed, the address of the instruction next to the skip instruction is specified irrespective of the contents of the skip instruction. If the skip conditions are satisfied, the instruction next to the skip instruction is executed and the address of the next instruction is specified.

#### 2. STACK

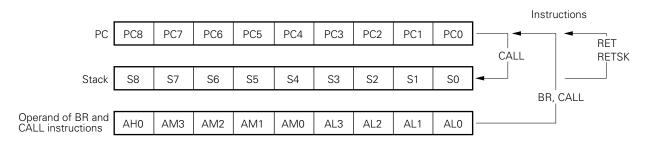

Stack of the  $\mu$ PD17104 is a register in which the return address of a program is saved when a subroutine call instruction is executed. One level of address stack is provided.

Fig. 2-1 shows the relationship between the PC, the stack, and the operand of BR and CALL instructions.

Fig. 2-1 Relationship between the PC, the Stack, and the Operand of BR and CALL Instructions

In Fig. 2-1, AHn, AMn, and ALn ( $0 \le n \le 3$ ) indicate bit positions in a 16-bit instruction as follows:

When the assembler (AS17K) is not used and a BR or CALL instruction is used, AH2 and AH1 must be set to 0.

Reset input clears all bits of the program counter to 0.

#### 3. PROGRAM MEMORY (ROM)

Fig. 3-1 shows the program memory (ROM) configuration.

As shown in the figure, the program memory has 512 words by 16 bits.

The program memory has been addressed in units of 16 bits. The addresses 0000H to 01FFH are specified by the program counter (PC).

Every instruction is a 1 word long, consisting of 16 bits. One instruction can therefore be stored at one address in program memory.

Address 0000H is used as a reset start address.

#### Fig. 3-1 Program Memory Map

#### 4. DATA MEMORY (RAM)

The data memory stores data of arithmetic/logic and control operations. Data can be always written to or read from it by means of instructions.

#### 4.1 CONFIGURATION OF THE DATA MEMORY (RAM)

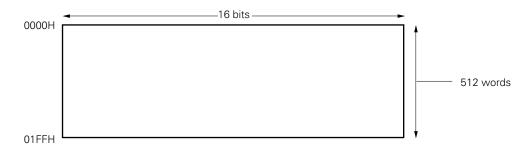

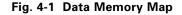

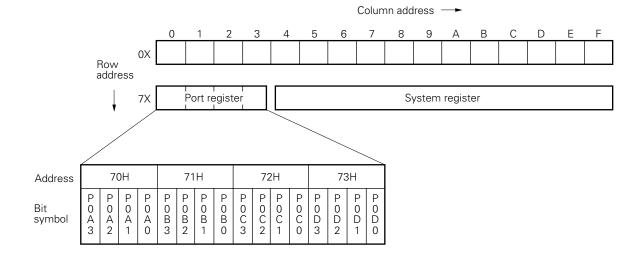

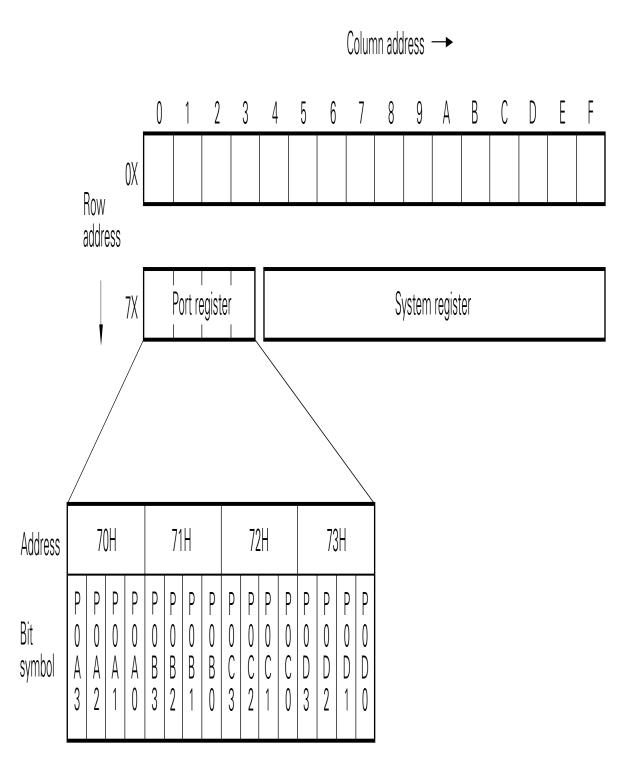

Fig. 4-1 shows the configuration of the data memory (RAM).

The data memory is configured in units of four bits, or "one nibble," and an address is assigned to each four bits of data. The high-order three bits are called the "row address," and the low-order four bits are called the "column address."

According to its functions, the data memory is divided into three blocks as shown below: General data memory, port register, and system register.

#### 4.1.1 Functions of the General Data Memory

The general data memory is a part of the data memory from which the system register (SYSREG) and port register are excluded. By executing a data memory manipulation instruction, a four-bit arithmetic operation and comparison, evaluation, and transfer between data on data memory and any immediate data can be executed with a single operation.

#### 4.1.2 Functions of the General Register

The general register indicates any identical row address (16 nibbles) in the data memory specified in the register pointer (RP) in the system register. Since the  $\mu$ PD17104 register pointer is always set to 0, the general data memory is also used as a general register. The general register can operate or transfer data to and from the data memory.

#### 4.1.3 Functions of the Port Register

The port register is used to set output data or to read the input data of input/output ports.

Once data is written to the port register corresponding to a port, the port is set to output mode and outputs the data unless another data is rewritten (the output mode is maintained until the port register is reset). Whenever a read instruction is executed for a port register, the read data indicates the states of the pins, not the value of the port register, regardless of whether the pins are in the input or output mode.

#### 4.1.4 Functions of the System Register

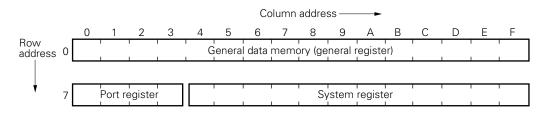

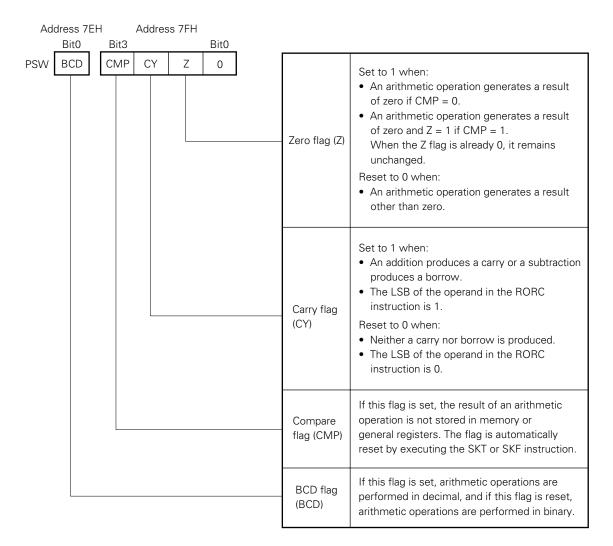

The system register controls the CPU. The program status word (PSWORD) is the only system register in the  $\mu$ PD17104.

#### Fig. 4-2 System Register Map

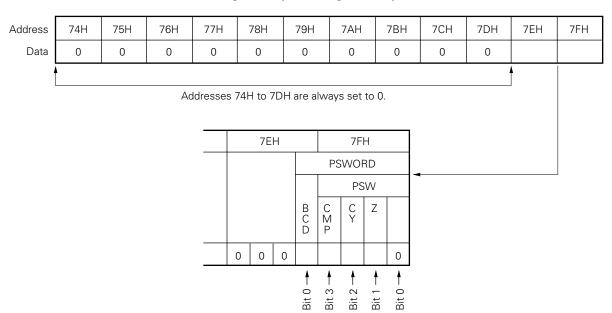

All four bits at address 7FH (PSW) and bit 0 at address 7EH are assigned to the program status word. The BCD flag is mapped in bit 0 at address 7EH, the CMP flag is mapped in bit 3 at address 7FH, the CY flag is mapped in bit 2, and the Z flag is mapped in bit 1 at address 7FH.

The high-order three bits at address 7EH and bit 0 at address 7FH are always set to 0.

#### Fig. 4-3 Configuration of the Program Status Word

Comparison instructions (SKE, SKNE, SKGE, or SKLT) do not change the state of the CY flag, but an arithmetic operation may affect the CY flag according to the result even if the CMP flag is set.

Each bit of the program status word is initialized to 0 when a reset signal is applied.

The Z flag in the program status word changes according to the set value of the CMP flag as listed in Table 4-1.

\*

#### Table 4-1 Change in Z Flag

| Conditions                                            | CMP = 0     | CMP = 1                |

|-------------------------------------------------------|-------------|------------------------|

| When arithmetic operation results in 0                | Z ← 1       | Z flag does not change |

| When arithmetic operation results in a non-zero value | $Z \gets 0$ | $Z \leftarrow 0$       |

While CMP is 1, if an arithmetic operation results in 0H when the value of the Z flag is 1, the Z flag does not change. If an arithmetic operation results in other than 0H, the Z flag is reset to 0 and remains intact even when a second arithmetic operation results in 0H.

After the CMP and Z flags are set to 1, subtraction and comparison are performed several times. Then, if the Z flag still indicates 1, all of the comparison operations showed a match, resulting in 0. If the Z flag is 0 after the comparison operations, a mismatch occurred in at least one comparison operation.

#### Example of 12-bit data comparison

; Is the 12-bit data stored in M001, M002, and M003 equal to 456H? CMP456:

| SET2  | CMP, Z   |                                                                       |

|-------|----------|-----------------------------------------------------------------------|

| SUB   | M001, #4 | ; Stores the data in M001, M002, and M003.                            |

| SUB   | M002, #5 | ; Does not damaged the data.                                          |

| SUB   | M003, #6 | ;                                                                     |

| ;CLR1 | СМР      |                                                                       |

| SKT   | Z        | ; Resets CMP automatically when the bit test instruction is executed. |

| BR    | DIFFER   | ; ≠ 456H                                                              |

| BR    | AGREE    | ; = 456H                                                              |

#### ★ 5. ALU BLOCK

The ALU is used for performing arithmetic operations, logical operations, bit evaluations, comparison evaluations, and rotations on 4-bit data.

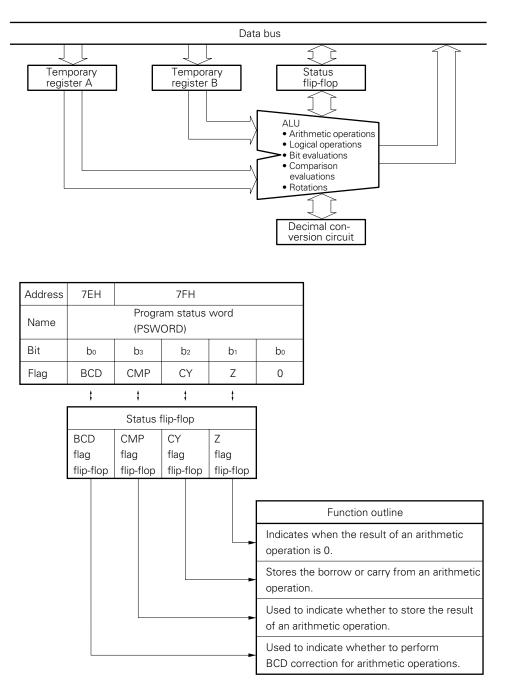

#### 5.1 ALU BLOCK CONFIGURATION

Fig. 5-1 shows the configuration of the ALU block.

As shown in Fig. 5-1, the ALU block consists of the main 4-bit data processor, temporary registers A and B, the status flip-flop for controlling the status of the ALU, and the decimal conversion circuit for use during arithmetic operations in BCD.

As shown in Fig. 5-1, the status flip-flop consists of the following flags: Zero flag flip-flop, carry flag flip-flop, compare flag flip-flop, and the BCD flag flip-flop.

Each flag in the status flip-flop corresponds directly to a flag in the program status word (PSWORD: addresses 7EH, 7FH) located in the system register. The flags in the program status word are the following: Zero flag (Z), carry flag (CY), compare flag (CMP), and the BCD flag (BCD).

#### 5.2 FUNCTIONS OF THE ALU BLOCK

Arithmetic operations, logical operations, bit evaluations, comparison evaluations, and rotations are performed using the instructions in the ALU block. Table 5-1 lists each arithmetic/logical instruction, evaluation instruction, and rotation instruction.

By using the instructions listed in Table 5-1, 4-bit arithmetic/logical operations, evaluations and rotations can be performed in a single instruction. Arithmetic operations in BCD can also be performed on one place in a single instruction.

#### 5.2.1 Functions of the ALU

The arithmetic operations consist of addition and subtraction. Arithmetic operations can be performed on the contents of the general register and data memory or on immediate data and the contents of data memory. Operations in binary are performed on four bits of data and operations in BCD are performed on one place.

Logical operations include ANDing, ORing, and XORing. Their operands can be general register contents and data memory contents, or data memory contents and immediate data.

Bit evaluation is used to determine whether bits in 4-bit data in data memory are 0 or 1.

Comparison evaluation is used to compare contents of data memory with immediate data. It is used to determine whether one value is equal to or greater than the other, less than the other, or if both values are equal or not equal.

Rotation is used to shift 4-bit data in the general register one bit in the direction of its least significant bit (rotation to the right).

#### Fig. 5-1 Configuration of the ALU

#### Table 5-1 List of ALU Instructions (1/2)

| ALU fu            | inction                   | Instruction | Operation                                                                                       | Explanation                                                                                                               |

|-------------------|---------------------------|-------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Arithme-<br>tic   | Addi-<br>tion             | ADD r, m    | (r) ← (r) + (m)                                                                                 | Adds contents of general register and data memory.<br>Result is stored in general register.                               |

| opera-<br>tions   |                           | ADD m, #n4  | (m) ← (m) + n4                                                                                  | Adds immediate data to contents of data memory. Result is stored in data memory.                                          |

|                   |                           | ADDC r, m   | $(r) \leftarrow (r) + (m) + CY$                                                                 | Adds contents of general register, data memory and carry flag. Result is stored in general register.                      |

|                   |                           | ADDC m, #n4 | $(m) \leftarrow (m) + n4 + CY$                                                                  | Adds immediate data, contents of data memory and carry flag. Result is stored in data memory.                             |

|                   | Sub-<br>trac-             | SUB r, m    | (r) ← (r) - (m)                                                                                 | Subtracts contents of data memory from contents of general register. Result is stored in general register.                |

|                   | tion                      | SUB m, #n4  | (m) ← (m) - n4                                                                                  | Subtracts immediate data from data memory. Result is stored in data memory.                                               |

|                   |                           | SUBC r, m   | (r) ← (r) - (m) - CY                                                                            | Subtracts contents of data memory and carry flag from contents of general register. Result is stored in general register. |

|                   |                           | SUBC m, #n4 | (m) ← (m) - n4 - CY                                                                             | Subtracts immediate data and carry flag from data memory. Result is stored in data memory.                                |

| Logical<br>opera- | Logical<br>OR             | OR r, m     | $(r) \leftarrow (r) \lor (m)$                                                                   | OR operation is performed on contents of general register<br>and data memory. Result is stored in general register.       |

| tions             |                           | OR m, #n4   | (m) ← (m) ∨ n4                                                                                  | OR operation is performed on immediate data and con-<br>tents of data memory. Result is stored in data memory.            |

|                   | Logical<br>AND            | AND r, m    | $(r) \leftarrow (r) \land (m)$                                                                  | AND operation is performed on contents of general register and data memory. Result is stored in general register.         |

|                   |                           | AND m, #n4  | (m) ← (m) ∧ n4                                                                                  | AND operation is performed on immediate data and contents of data memory. Result is stored in data memory.                |

|                   | Logical<br>XOR            | XOR r, m    | (r) ← (r) <del>∀</del> (m)                                                                      | XOR operation is performed on contents of general register<br>and data memory. Result is stored in general register.      |

|                   |                           | XOR m, #n4  | (m) ← (m) <del>∀</del> n4                                                                       | XOR operation is performed on immediate data and contents of data memory. Result is stored in data memory.                |

| Bit<br>evalua-    | True                      | SKT m, #n   | $CMP \leftarrow 0$ , if (m) $\land n = n$ ,<br>then skip                                        | Skips next instruction if all bits in data memory specified by n are TRUE (1). Result is not stored.                      |

| tion              | False                     | SKF m, #n   | $CMP \leftarrow 0$ , if (m) $\land n = 0$ ,<br>then skip                                        | Skips next instruction if all bits in data memory specified by n are FALSE (0). Result is not stored.                     |

| Com-<br>parison   | Equal                     | SKE m, #n4  | (m) - n4, skip if zero                                                                          | Skips next instruction if immediate data equals contents of data memory. Result is not stored.                            |

| evalua-<br>tion   | Not<br>equal              | SKNE m, #n4 | (m) - n4, skip if not<br>zero                                                                   | Skips next instruction if immediate data is not equal to contents of data memory. Result is not stored.                   |

|                   | 2                         | SKGE m, #n4 | (m) - n4, skip if not<br>borrow                                                                 | Skips next instruction if contents of data memory is greater<br>than or equal to immediate data. Result is not stored.    |

|                   | <                         | SKLT m, #n4 | (m) - n4, skip if borrow                                                                        | Skips next instruction if contents of data memory is less than immediate data. Result is not stored.                      |

| Rotation          | Rotate<br>to the<br>right | RORC r      | $  (CY) \rightarrow (r)_{b3} \rightarrow (r)_{b2} \rightarrow (r)_{b1} \rightarrow (r)_{b0} ] $ | Rotate contents of the general register along with the CY flag to the right. Result is stored in general register.        |

| ALU function          |                            | Operation                       | n depending on the                             | program                                     | status word (PSWORD)                                                            |

|-----------------------|----------------------------|---------------------------------|------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|

| Arithmetic operation  |                            |                                 |                                                |                                             |                                                                                 |

|                       | Value in<br>BCD flag       | Value in<br>CMP flag            | Operation                                      | CY flag                                     | Z flag                                                                          |

|                       | 0                          | 0                               | Store result of binary operation               | Set (1)<br>when                             | Set (1) when result of operation is 0000B, otherwise reset (0).                 |

|                       | 0                          | 1                               | Do not store<br>result of binary<br>operation  | carry or<br>borrow<br>is gener-             | Status maintained when result<br>of operation is 0000B, otherwise<br>reset (0). |

|                       | 1                          | 0                               | Store result of decimal operation              | ated,<br>otherwise<br>reset (0).            | Set (1) when result of operation<br>is 0000B, otherwise reset (0).              |

|                       | 1                          | 1                               | Do not store<br>result of decimal<br>operation |                                             | Status maintained when result<br>of operation is 0000B, otherwise<br>reset (0). |

|                       |                            |                                 |                                                |                                             |                                                                                 |

| Logical<br>operations |                            |                                 |                                                | Don't care                                  |                                                                                 |

|                       | Don't care<br>(maintained) | Don't care<br>(maintained)      | No change                                      | (main-<br>tained)                           | Don't care<br>(maintained)                                                      |

|                       |                            |                                 |                                                |                                             |                                                                                 |

|                       |                            | 1<br>1<br>1<br>1<br>1<br>1      | 1<br>1<br>1<br>1<br>1<br>1                     |                                             |                                                                                 |

|                       |                            | <br> <br> <br> <br> <br>        |                                                |                                             |                                                                                 |

|                       |                            | 1<br>1<br>1<br>1<br>1<br>1      |                                                |                                             |                                                                                 |

|                       |                            |                                 |                                                |                                             |                                                                                 |

| Bit evaluation        | Don't care                 |                                 |                                                | Don't care                                  | Don't care                                                                      |

|                       | (maintained)               | Reset                           | No change                                      | (main-<br>tained)                           | (maintained)                                                                    |

| Comparison            |                            |                                 |                                                |                                             |                                                                                 |

| evaluation            | Don't care<br>(maintained) | Don't care<br>(maintained)      | No change                                      | Don't care<br>(main-<br>tained)             | Don't care<br>(maintained)                                                      |

|                       |                            | 1<br>1<br>1<br>1<br>1<br>1      |                                                |                                             |                                                                                 |

|                       |                            | 1<br>1<br>1<br>1<br>1<br>1<br>1 |                                                |                                             |                                                                                 |

| Rotation              | Don't care<br>(maintained) | Don't care<br>(maintained)      | No change                                      | Value in b₀<br>of the gen-<br>eral register | Don't care<br>(maintained)                                                      |

#### Table 5-1 List of ALU Instructions (2/2)

#### 5.2.2 Functions of Temporary Registers A and B

Temporary registers A and B are needed for processing of 4-bit data. These registers are used for temporary storage of the first and second data operands of an instruction.

#### 5.2.3 Functions of the Status Flip-Flop

The status flip-flop is used for controlling operation of the ALU and for storing data which has been processed. Each flag in the status flip-flop corresponds directly to a flag in the program status word (PSWORD) located in the system register. This means that when a flag in the system register is manipulated it is the same as manipulating a flag in the status flip-flop. Each flag in the program status word is described below.

#### (1) Z flag

This flag is set (1) when the result of an arithmetic operation is 0000B, otherwise it is reset (0). However, as described below, depending on the status of the CMP flag, the conditions which cause this flag to be set (1) can be changed.

#### (i) When CMP = 0

Z flag is set (1) when the result of an arithmetic operation is 0000B, otherwise it is reset (0).

#### (ii) When CMP = 1

The previous state of the Z flag is maintained when the result of an arithmetic operation is 0000B, otherwise it is reset (0). Only affected by arithmetic operations.

#### (2) CY flag

This flag is set (1) when a carry or borrow is generated in the result of an arithmetic operation, otherwise it is reset (0).

When an arithmetic operation is being performed using a carry or borrow, the operation is performed using the CY flag as the least significant bit. When a rotation (RORC instruction) is performed, the contents of the CY flag becomes the most significant bit (bit b<sub>3</sub>) of the general register and the least significant bit of the general register is stored in the CY flag.

Only affected by arithmetic operations and rotations.

#### (3) CMP flag

When the CMP flag is set (1), the result of an arithmetic operation is not stored in either the general register or data memory.

When the bit evaluation instruction is performed, the CMP flag is reset (0).

The CMP flag does not affect comparison evaluations, logical operations, or rotations.

#### (4) BCD flag

When the BCD flag is set (1), all arithmetic operations are performed in BCD. When the flag is reset (0), all operations are performed in 4-bit binary.

The BCD flag does not affect logical operations, bit evaluations, comparison evaluations, or rotations.

These flags can also be set through direct manipulation of the values in the program status word (PSWORD). When the flags in the program status word are manipulated, the corresponding flag in the status flip-flop is also manipulated.

#### 5.2.4 Performing Operations in 4-Bit Binary

When the BCD flag is set to 0, arithmetic operations are performed in 4-bit binary.

#### 5.2.5 Performing Operations in BCD

When the BCD flag is set to 1, arithmetic operations are performed in BCD. Table 5-2 shows the differences in the results of operations performed in 4-bit binary and in BCD. When the result of an addition in BCD is equal to or greater than 20, or the result of a subtraction in BCD is outside of the range -10 to +9, a value of 1010B (0AH) or higher is stored as the result (shaded area in Table 5-2).

| Operation | Addition in<br>4-bit binary |                  | Addition in<br>BCD |                  |

|-----------|-----------------------------|------------------|--------------------|------------------|

| result    | CY                          | Operation result | СҮ                 | Operation result |

| 0         | 0                           | 0000             | 0                  | 0000             |

| 1         | 0                           | 0001             | 0                  | 0001             |

| 2         | 0                           | 0010             | 0                  | 0010             |

| 3         | 0                           | 0011             | 0                  | 0011             |

| 4         | 0                           | 0100             | 0                  | 0100             |

| 5         | 0                           | 0101             | 0                  | 0101             |

| 6         | 0                           | 0110             | 0                  | 0110             |

| 7         | 0                           | 0111             | 0                  | 0111             |

| 8         | 0                           | 1000             | 0                  | 1000             |

| 9         | 0                           | 1001             | 0                  | 1001             |

| 10        | 0                           | 1010             | 1                  | 0000             |

| 11        | 0                           | 1011             | 1                  | 0001             |

| 12        | 0 1100 1                    |                  | 1                  | 0010             |

| 13        | 0                           | 1101             | 1                  | 0011             |

| 14        | 0                           | 1110             | 1                  | 0100             |

| 15        | 0                           | 1111             | 1                  | 0101             |

| 16        | 1                           | 0000             | 1                  | 0110             |

| 17        | 1                           | 0001             | 1                  | 0111             |

| 18        | 1                           | 0010             | 1                  | 1000             |

| 19        | 1                           | 0011             | 1                  | 1001             |

| 20        | 1                           | 0100             | 1                  | 1110             |

| 21        | 1                           | 0101             | 1                  | 1111             |

| 22        | 1                           | 0110             | 1                  | 1100             |

| 23        | 1                           | 0111             | 1                  | 1101             |

| 24        | 1                           | 1000             | 1                  | 1110             |

| 25        | 1                           | 1001             | 1                  | 1111             |

| 26        | 1                           | 1010             | 1                  | 1100             |

| 27        | 1                           | 1011             | 1                  | 1101             |

| 28        | 1                           | 1100             | 1                  | 1010             |

| 29        | 1                           | 1101             | 1                  | 1011             |

| 30        | 1                           | 1110             | 1                  | 1100             |

| 31        | 1                           | 1111             | 1                  | 1101             |

#### Subtraction in Subtraction in 4-bit binary BCD Operation Operation Operation CY CY result result -16 -15 -14 -13 -12 -11 -10 -9 -8 -7 -6 -5 -4 -3 -2 -1

#### Table 5-2 Results of Arithmetic Operations Performed in 4-Bit Binary and BCD

#### 5.2.6 Performing Operations in the ALU Block

When arithmetic operations, logical operations, bit evaluations, comparison evaluations or rotations in a program are executed, the first data operand is stored in temporary register A and the second data operand is stored in temporary register B.

The first data operand is four bits of data used to specify the contents of an address in the general register or data memory. The second data operand is four bits of data used to either specify the contents of an address in data memory or to be used as an immediate value. For example, in the instruction

ADD r, m Second data operand First data operand

the first data operand, r, is used to specify the contents of an address in the general register. The second data operand, m, is used to specify the contents of an address in data memory. In the instruction

#### ADD m, #n4

the first data operand, m, is used to specify an address in data memory. The second operand, #n4, is immediate data. In the rotation instruction

#### RORC r

only the first data operand, r (used to specify the contents of an address in the general register) is used.

Next, using the data stored in temporary registers A and B, the ALU executes the operation specified by the instruction (arithmetic operation, logical operation, bit evaluation, comparison evaluation, or rotation). When the instruction being executed is an arithmetic operation, logical operation, or rotation, the data processed by the ALU is stored in the location specified by the first data operand (general register address or data memory address) and the operation terminates. When the instruction being executed is a bit evaluation or comparison evaluation, the result processed by the ALU is used to determine whether or not to skip the next instruction (whether to treat next instruction as a no operation instruction: NOP) and the operation terminates.

Caution should be taken with regard to the following points:

- (1) Arithmetic operations are affected by the CMP and BCD flags in the program status word.

- (2) Logical operations are not affected by the CMP or BCD flag in the program status word. Logical operations do not affect the Z or CY flags.

- (3) Bit evaluation causes the CMP flag in the program status word to be reset.

#### 5.3 ARITHMETIC OPERATIONS (ADDITION AND SUBTRACTION IN 4-BIT BINARY AND BCD)

As shown in Table 5-3, arithmetic operations consist of addition, subtraction, addition with carry, and subtraction with borrow. These instructions are ADD, ADDC, SUB, and SUBC.

The ADD, ADDC, SUB, and SUBC instructions are further divided into addition and subtraction of the general register and data memory and addition and subtraction of data memory and immediate data. When the operands r and m are used, addition or subtraction is performed using the general register and data memory. When the operands m and #n4 are used, addition or subtraction is performed using data memory and immediate data.

Arithmetic operations are affected by the status flip-flop and the program status word (PSWORD) in the system register. The BCD flag in the program status word (PSWORD) is used to specify whether arithmetic operations are to be performed in 4-bit binary or in BCD. The CMP flag is used to specify whether or not the results of arithmetic operations are to be stored.

Sections **5.3.1 to 5.3.4** explain the relationship between each command and the program status word (PSWORD).

| Arithmetic | Addition    | Addition Without carry ADD | General register and data memory | ADD r, m    |

|------------|-------------|----------------------------|----------------------------------|-------------|

| operation  |             |                            | Data memory and immediate data   | ADD m, #n4  |

|            |             | With carry ADDC            | General register and data memory | ADDC r, m   |

|            |             |                            | Data memory and immediate data   | ADDC m, #n4 |

|            | Subtraction | Without borrow SUB         | General register and data memory | SUB r, m    |

|            |             |                            | Data memory and immediate data   | SUB m, #n4  |

|            |             | With borrow SUBC           | General register and data memory | SUBC r, m   |

|            |             |                            | Data memory and immediate data   | SUBC m, #n4 |

#### **Table 5-3 Types of Arithmetic Operations**

#### 5.3.1 Addition and Subtraction When CMP = 0 and BCD = 0

Addition and subtraction are performed in 4-bit binary and the result is stored in the general register or data memory.

When the result of the operation is greater than 1111B (carry generated) or less than 0000B (borrow generated), the CY flag is set (1); otherwise it is reset (0).

When the result of the operation is 0000B, the Z flag is set (1) regardless of whether there is carry or borrow; otherwise it is reset (0).

#### 5.3.2 Addition and Subtraction When CMP = 1 and BCD = 0

Addition and subtraction are performed in 4-bit binary.

However, because the CMP flag is set (1), the result of the operation is not stored in either the general register or data memory.

When there is a carry or borrow in the result of the operation, the CY flag is set (1); otherwise it is reset (0).

When the result of the operation is 0000B, the previous state of the Z flag is maintained; otherwise it is reset (0).

#### 5.3.3 Addition and Subtraction When CMP = 0 and BCD = 1

BCD operations are performed.

The result of the operation is stored in the general register or data memory. When the result of the operation is greater than 1001B (9D) or less than 0000B (0D), the carry flag is set (1), otherwise it is reset (0).

When the result of the operation is 0000B (0D), the Z flag is set (1), otherwise it is reset (0).

Operations in BCD are performed by first computing the result in binary and then by using the decimal conversion circuit to convert the result to decimal. For information concerning the binary to decimal conversion, see Table 5-2 in Section **5.2.5**.

In order for operations in BCD to be performed properly, note the following:

(1) Result of an addition must be in the range 0D to 19D.

(2) Result of a subtraction must be in the range 0D to 9D, or in the range -10D to -1D.

The following shows which value is considered the CY flag in the range 0D to 19D (shown in hexadecimal): 0, 0000B to 1, 0011B

ĉŶ

The following shows which value is considered the CY flag in the range -10D to -1D (shown in hexadecimal): 1, 0110B to 1, 1111B

CŶ CŶ

ĆŶ

When operations in BCD are performed outside of the limits of (1) and (2) stated above, the CY flag is set (1) and the result of operation is output as a value greater than or equal to 1010B (0AH).

#### 5.3.4 Addition and Subtraction When CMP = 1 and BCD = 1

BCD operations are performed.

The result is not stored in either the general register or data memory.

In other words, the operations specified by CMP = 1 and BCD = 1 are both performed at the same time.

| Example | MOV  | RPL, #0001B | ; | Sets the BCD flag (BCD = 1).                                    |

|---------|------|-------------|---|-----------------------------------------------------------------|

|         | MOV  | PSW, #1010B | ; | Sets the CMP and Z flag (CMP = 1, Z = 1) and resets the CY flag |

|         |      |             | ; | (CY = 0).                                                       |

|         | SUB  | M1, #0001B  | ; | #                                                               |

|         | SUBC | M2, #0010B  | ; | \$                                                              |

|         | SUBC | M3, #0011B  | ; | %                                                               |

|         |      |             |   |                                                                 |

By executing the instructions in steps numbered #, \$, and %, the twelve bits in memory locations M1, M2, and M3 and the immediate data (321) can be compared in decimal.

#### 5.3.5 Warnings Concerning Use of Arithmetic Operations

When performing arithmetic operations with the program status word (PSWORD), caution should be taken with regard to the result of the operation being stored in the program status word.

Normally, the CY and Z flags in the program status word are set (1) or reset (0) according to the result of the arithmetic operation being executed. However, when an arithmetic operation is performed on the program status word itself, the result is stored in the program status word. This means that there is no way to determine if there is a carry or borrow in the result of the operation nor if the result of the operation is zero.

However, when the CMP flag is set (1), results of arithmetic operations are not stored. Therefore, even in the above case, the CY and Z flags will be properly set (1) or reset (0) according to the result of the operation.

#### 5.4 LOGICAL OPERATIONS

As shown in Table 5-4, logical operations consist of logical OR, logical AND, and logical XOR. Accordingly, the logical operation instructions are OR, AND, and XOR.

The OR, AND, and XOR instructions can be performed on either the general register and data memory, or on data memory and immediate data. The operands of these instructions are specified in the same way as for arithmetic operations ("r, m" or "m, #n4").

Logical operations are not affected by the BCD or CMP flags in the program status word (PSWORD). The operations do not affect the CY and Z flags at all.

#### **Table 5-4 Logical Operations**

| Logical   | Logical OR  | General register and data memory | OR r, m    |

|-----------|-------------|----------------------------------|------------|

| operation |             | Data memory and immediate data   | OR m, #n4  |

|           | Logical AND | General register and data memory | AND r, m   |

|           |             | Data memory and immediate data   | AND m, #n4 |

|           | Logical XOR | General register and data memory | XOR r, m   |

|           |             | Data memory and immediate data   | XOR m, #n4 |

| Table 5-5 | Table of | True | Values | for | Logical | Operations |

|-----------|----------|------|--------|-----|---------|------------|

|-----------|----------|------|--------|-----|---------|------------|

| Logical AND<br>C = A AND B |   |    | Logical OR<br>C = A OR B |   |   | Logical XOR<br>C = A XOR B |   |   |

|----------------------------|---|----|--------------------------|---|---|----------------------------|---|---|

|                            |   | ЬВ | U U                      |   |   | C =                        |   |   |

| А                          | В | С  | А                        | В | С | А                          | В | С |

| 0                          | 0 | 0  | 0                        | 0 | 0 | 0                          | 0 | 0 |

| 0                          | 1 | 0  | 0                        | 1 | 1 | 0                          | 1 | 1 |

| 1                          | 0 | 0  | 1                        | 0 | 1 | 1                          | 0 | 1 |

| 1                          | 1 | 1  | 1                        | 1 | 1 | 1                          | 1 | 0 |

#### 5.5 BIT EVALUATIONS

As shown in Table 5-6, there are both TRUE (1) and FALSE (0) bit evaluation instructions.

The SKT instruction skips the next instruction when a bit is evaluated as TRUE (1) and the SKF instruction skips the next instruction when a bit is evaluated as FALSE (0).

The SKT and SKF instructions can only be used with data memory.

Bit evaluations are not affected by the BCD flag in the program status word (PSWORD). The evaluations do not affect the CY and Z flags at all. However, when an SKT or SKF instruction is executed, the CMP flag is reset (0).

Sections 5.5.1 and 5.5.2 explain TRUE (1) and FALSE (0) bit evaluations.

| Table 5-6 Bit Evaluation Instruction |

|--------------------------------------|

|--------------------------------------|

| Bit evaluation | TRUE (1) bit evaluation<br>SKT m, #n  |

|----------------|---------------------------------------|

|                | FALSE (0) bit evaluation<br>SKF m, #n |

#### 5.5.1 TRUE (1) Bit Evaluation

The TRUE (1) bit evaluation instruction (SKT m, #n) is used to determine whether or not the bits specified by n in the four bits of data memory m are TRUE (1). When all bits specified by n are TRUE (1), this instruction causes the next instruction to be skipped.

| Example | MOV | M1, | #1011B |     |  |

|---------|-----|-----|--------|-----|--|

|         | SKT | M1, | #1011B | ;#  |  |

|         | BR  | А   |        |     |  |

|         | BR  | В   |        |     |  |

|         | SKT | M1, | #1101B | ;\$ |  |

|         | BR  | С   |        |     |  |

|         | BR  | D   |        |     |  |

In this example, bits  $b_3$ ,  $b_1$ , and  $b_0$  of data memory M1 are evaluated in step number #. Because all the bits are TRUE (1), the program branches to B. In step number \$, bits  $b_3$ ,  $b_2$ , and  $b_0$  of data memory M1 are evaluated. Since  $b_2$  of data memory M1 is FALSE (0), the program branches to C.

#### 5.5.2 FALSE (0) Bit Evaluation

The FALSE (0) bit evaluation instruction (SKF m, #n) is used to determine whether or not the bits specified by n in the four bits of data memory m are FALSE (0). When all bits specified by n are FALSE (0), this instruction causes the next instruction to be skipped.

| Example | MOV | M1, | #1001B |   |    |

|---------|-----|-----|--------|---|----|

|         | SKF | M1, | #0110B | ; | #  |

|         | BR  | А   |        | ; |    |

|         | BR  | В   |        | ; |    |

|         | SKF | M1, | #1110B | ; | \$ |

|         | BR  | С   |        | ; |    |

|         | BR  | D   |        | ; |    |

In this example, bits b<sub>2</sub> and b<sub>1</sub> of data memory M1 are evaluated in step number #. Because both bits are FALSE (0), the program branches to B. In step number \$, bits b<sub>3</sub>, b<sub>2</sub>, and b<sub>1</sub> of data memory M1 are evaluated. Since b<sub>3</sub> of data memory M1 is TRUE (1), the program branches to C.

#### 5.6 COMPARISON EVALUATIONS

As shown in Table 5-7, there are comparison evaluation instructions for determining if one value is "equal to", "not equal to", "greater than or equal to", or "less than" another.

The SKE instruction is used to determine if two values are equal. The SKNE instruction is used to determine two values are not equal. The SKGE instruction is used to determine if one value is greater than or equal to another and the SKLT instruction is used to determine if one value is less than another.

The SKE, SKNE, SKGE, and SKLT instructions perform comparisons between a value in data memory and immediate data. In order to compare values in the general register and data memory, a subtraction instruction is performed according to the values in the CMP and Z flags in the program status word (PSWORD). For more information concerning comparison of the general register and data memory, see Section **5.3**.

Comparison evaluations are not affected by the BCD or CMP flags in the program status word (PSWORD). The evaluations do not affect the CY and Z flags at all.

Sections **5.6.1 to 5.6.4** explain the "equal", "not equal", "greater than or equal", and "less than" comparison evaluations.

| Comparison<br>evaluation | Equal<br>SKE m, #n4                  |

|--------------------------|--------------------------------------|

|                          | Not equal<br>SKNE m, #n4             |

|                          | Greater than or equal<br>SKGE m, #n4 |

|                          | Less than<br>SKLT m, #n4             |

#### Table 5-7 Comparison Evaluation Instructions

#### 5.6.1 "Equal" Evaluation

The "equal" evaluation instruction (SKE m, #n4) is used to determine if immediate data and the contents of a location in data memory are equal.

This instruction causes the next instruction to be skipped when the immediate data and the contents of data memory are equal.

```

Example MOV

M1,

#1010B

SKE

M1,

#1010B

; #

BR

А

BR

В

;

SKE

M1,

#1000B

;$

С

BR

D

BR

```

In this example, because the contents of data memory M1 and immediate data 1010B in step number # are equal, the program branches to B. In step number \$, because the contents of data memory M1 and immediate data 1000B are not equal, the program branches to C.

#### 5.6.2 "Not Equal" Evaluation

The "not equal" evaluation instruction (SKNE m, #n4) is used to determine if immediate data and the contents of a location in data memory are not equal.

This instruction causes the next instruction to be skipped when the immediate data and the contents of data memory are not equal.

```

#1010B

Example MOV

M1,

SKNE

M1,

#1000B

; #

BR

А

BR

В

;

SKNE

M1,

#1010B

; $

С

BR

BR

D

```

In this example, because the contents of data memory M1 and immediate data 1000B in step number # are not equal, the program branches to B. In step number \$, because the contents of data memory M1 and immediate data 1010B are equal, the program branches to C.

#### 5.6.3 "Greater Than or Equal" Evaluation

The "greater than or equal" evaluation instruction (SKGE m, #n4) is used to determine if the contents of a location in data memory is a value greater than or equal to the value of the immediate data operand. If the value in data memory is greater than or equal to that of the immediate data, this instruction causes the next instruction to be skipped.

```

Example MOV

M1,

#1000B

SKGE

M1,

#0111B

; #

BR

А

BR

В

;

SKGE

M1,

#1000B

; $

С

BR

BR

D

;

SKGE

M1,

#1001B

; %

BR

Е

BR

F

```

In this example, the program will first branch to B since the value in data memory is larger than that of the immediate data (#). Next it will branch to D since the value in data memory is equal to that of the immediate data (\$). Last it will branch to E since the value in data memory is less than that of the immediate data (%).

#### 5.6.4 "Less Than" Evaluation

The "less than" evaluation instruction (SKLT m, #n4) is used to determine if the contents of a location in data memory is a value less than that of the immediate data operand. If the value in data memory is less than that of the immediate data, this instruction causes the next instruction to be skipped.

```

Example MOV

M1,

#1000B

SKLT

M1,

#1001B

; #

BR

А

BR

В

;

SKLT

M1,

#1000B

; $

BR

С

BR

D

SKLT

M1,

#0111B

; %

Е

BR

BR

F

```

In this example, the program will first branch to B since the value in data memory is less than that of the immediate data (#). Next it will branch to C since the value in data memory is equal to that of the immediate data (\$). Last it will branch to E since the value in data memory is greater than that of the immediate data (%).

## NEC

#### 5.7 ROTATIONS

There are rotation instructions for rotation to the right and for rotation to the left.

The RORC instruction is used for rotation to the right.

The RORC instruction can only be used with the general register.

Rotation using the RORC instruction is not affected by the BCD or CMP flags in the program status word (PSWORD). The rotation does not affect the Z flag at all.

Rotation to the left is performed by using the addition instruction ADDC.

Sections 5.7.1 and 5.7.2 explain rotation.

#### 5.7.1 Rotation to the Right

The instruction used for rotation to the right (RORC r) rotates the contents of the general register in the direction of its least significant bit.

When this instruction is executed, the contents of the CY flag becomes the most significant bit of the general register (bit b<sub>3</sub>) and the least significant bit of the general register (bit b<sub>3</sub>) is placed in the CY flag.

```

Examples 1. MOV PSW, #0100B ; Sets CY flag to 1.

MOV R1, #1001B

RORC R1 ; #

```

When these instructions are executed, the following operation is performed.

CY flag b₃ b₂ b₁ b₀ ┌╾ 1 ─────1 ──1 ──0 ──0 ──

Basically, when rotation to the right is performed, the following operation is executed:

CY flag  $\rightarrow$  b3, b3  $\rightarrow$  b2, b2  $\rightarrow$  b1, b1  $\rightarrow$  b0, b0  $\rightarrow$  CY flag.

2. MOV PSW, #0000B ; Resets CY flag to 0. MOV R1, #1000B MOV R2, #0100B MOV R3, #0010B RORC R1 RORC R2 RORC R3

The program code above rotates the twelve bits in R1, R2, and R3 to the right.

#### 5.7.2 Rotation to the Left

Rotation to the left is performed by using the addition instruction, "ADDC r, m".

| Example | MOV  | PSW,   | #0000B | ; Resets CY flag to 0. |

|---------|------|--------|--------|------------------------|

|         | MOV  | R1,    | #1000B |                        |

|         | MOV  | R2,    | #0100B |                        |

|         | MOV  | R3,    | #0010B |                        |

|         | ADDC | R3, R3 | }      |                        |

|         | ADDC | R2, R2 | !      |                        |

|         | ADDC | R1, R1 |        |                        |

The program code above rotates the twelve bits in R1, R2, and R3 to the left.

#### 6. PORTS

#### 6.1 PORT 0A (P0A<sub>0</sub> TO P0A<sub>3</sub>)

Port 0A is a four-bit input/output port. CMOS (push-pull) outputs appear on these pins.

Input and output are set in units of nibbles. The input mode is set at reset, and the output mode is set by writing data to the port register in address 70H of the data memory. The output mode is maintained until the system is reset.

Output to the port is executed via the port register. Once data is written to the port register, all pins of the port 0A are placed in the output mode to continue to output written data. The data is retained until new data is written to the register.

Whenever the port register is read, the read data indicates the states of the pins<sup>Note</sup>, not the contents of the port register, regardless of whether the pins are in the input or output mode. In this case, the contents of the port register remain unchanged.

#### 6.2 PORT 0B (P0B0/RLSHALT, P0B1/RLSSTOP, P0B2, P0B3)

Port 0B is a four-bit input/output port. Only N-ch open-drain outputs appear on the pins of port 0B. The N-ch open-drain output mode allows application of 9 V, so it can be used for interfacing with a circuit operating on a different power supply voltage.

Input and output are set in units of nibbles. The input mode is set at reset, and the output mode is set by writing data to the port register in address 71H of the data memory. The output mode is maintained until the system is reset.

Output to the port is executed via the port register. Once data is written to the port register, all pins of port 0B are placed in the output mode to continue to output written data. The data is retained unless new data is written to the register.

Writing 1 to the port register makes the N-ch open-drain output pin high-impedance. Therefore, the pin which outputs 1 can be used as an input pin.

Whenever the port register is read, the read data indicates the states of the pins<sup>Note</sup>, not the contents of the port register, regardless of whether the pins are in the input or output mode. In this case, the contents of the port register remain unchanged.

A P0B<sub>0</sub> input signal releases the HALT mode as a pseudo interrupt. P0B<sub>1</sub> input signal releases the STOP mode as a pseudo interrupt. (See **Section 7**.)

#### 6.3 PORT OC (POC<sub>0</sub> TO POC<sub>3</sub>)

Port 0C is a four-bit input/output port. CMOS (push-pull) outputs appear on those pins.

Input and output are set in units of nibbles. The input mode is set at reset, and the output mode is set by writing data to the port register in address 72H of the data memory. The output mode is maintained until the system is reset.

Output to the port is executed via the port register. Once data is written to the port register, all pins of the port 0C are placed in the output mode to continue to output written data. The data is retained unless new data is written to the register.

Whenever the port register is read, the read data indicates the states of the pins<sup>Note</sup>, not the contents of the port register, regardless of whether the pins are in the input or output mode. In this case, the contents of the port register remain unchanged.

**Note** In the output mode, design an external circuit appropriately depending on the output data.

#### 6.4 PORT 0D (P0D<sub>0</sub> TO P0D<sub>3</sub>)

Port 0D is a four-bit input/output port. CMOS (push-pull) outputs appear on these pins.

Input and output are set in units of nibbles. The input mode is set at reset, and the output mode is set by writing data to the port register in address 73H of the data memory. The output mode is maintained until the system is reset.

Output to the port is executed via the port register. Once data is written to the port register, all pins of the port 0D are placed in the output mode to continue to output written data. The data is retained until new data is written to the register.

Whenever the port register is read, the read data indicates the states of the pins<sup>Note</sup>, not the contents of the port register, regardless of whether the pins are in the input or output mode. In this case, the contents of the port register remain unchanged.

Note In the output mode, design an external circuit appropriately depending on the output data.

#### Fig. 6-1 Port Register Map

#### 6.5 Notes on Manipulating Port Registers

The states of the I/O port pins of the  $\mu$ PD17104 can be read even when the port pins have been set to output mode.

When a port register is manipulated with a built-in macro instruction (such as SETn or CLRn) or an AND, OR, or XOR instruction, the states of those pins for which the state should remain unchanged may change unexpectedly.

Especially when using some of the port 0B pins (N-ch open-drain outputs) as input pins, with the remaining port 0B pins being used as output pins, always take the possibility of this change in the states of the pins into consideration.

When a CLR1 P0B2 instruction (identical to an AND 71H, #1011B instruction) is applied to the port 0B pins, the corresponding port register and internal states are changed, as shown in Fig. 6-2.

Assume that the states of port 0B are those shown in Fig. 6-2 #. Pins  $P0B_3$  and  $P0B_2$ , used as output pins, output high level, while pins  $P0B_1$  and  $P0B_0$ , used as input pins, receive low level.

It is required that high level be output, inside the chip, from the port 0B pins to be used as input pins. Although the  $\mu$ PD17103,  $\mu$ PD17103L,  $\mu$ PD17107, and  $\mu$ PD17107L do not support pin P0B<sub>3</sub>, it is virtually assumed to exist within a program.

When a CLR1 P0B2 instruction is executed to set pin  $P0B_2$  to low, the states of the port 0B pins change us shown in Fig. 6-2 \$. The port register changes such that pins  $P0B_1$  and  $P0B_0$ , required to output high level, actually output low level. This is because the CLR1 P0B2 instruction has been applied to the states of the port 0B pins, but not to the states of the port register.

To prevent this problem, use another instruction, such as a MOV instruction, to specify the states of all port 0B pins, not merely the states of those pins whose states are to be changed. In this example, it is recommended that a MOV 71H, 1011B instruction be used to set only pin P0B<sub>2</sub> to low.

#### Fig. 6-2 Changes in the Port Register According to the Execution of a CLR1 POB2 Instruction

| State         | P0B₃     | P0B <sub>2</sub> | P0B1      | P0B₀      |

|---------------|----------|------------------|-----------|-----------|

| Port register | 1        | 1                | 1         | 1         |

| Internal      | H output | H output         | H output  | H output  |

| Pin           | Н        | Н                | L (input) | L (input) |

# Executing a CLR1 P0B2 instruction [AND 71H, #1011B]

\$ After the instruction is executed

# Before the instruction is executed

| State         | P0B₃     | P0B <sub>2</sub> | P0B1     | P0B₀     |

|---------------|----------|------------------|----------|----------|

| Port register | 1        | 0                | 0        | 0        |

| Internal      | H output | L output         | L output | L output |

| Pin           | Н        | L                | L        | L        |

H: High level, L: Low level

#### 7. STANDBY FUNCTIONS

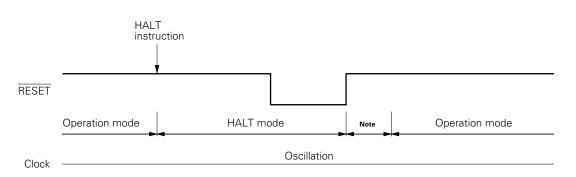

The  $\mu$ PD17104 provides two standby modes, the HALT mode and the STOP mode.

#### 7.1 HALT MODE

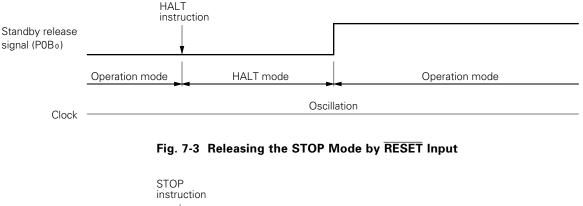

The HALT mode stops the program counter (PC) while allowing the system clock to continue operating. The HALT mode can be entered with the HALT instruction, and can be released by a reset signal ( $\overline{\text{RESET}}$ ) or high-level input to the P0B<sub>0</sub> pin. When the HALT mode is released by a high-level signal input to the P0B<sub>0</sub> pin, the system does not wait for the system clock oscillation to settle. The instruction immediately after the HALT instruction is executed.

When the HALT mode is released forcibly by the reset signal (RESET), normal system reset occurs, and the program starts at address 0H.

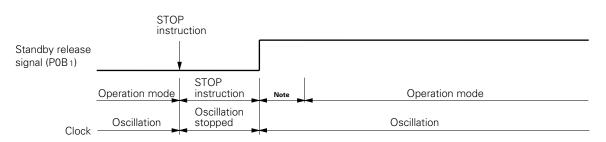

#### 7.2 STOP MODE

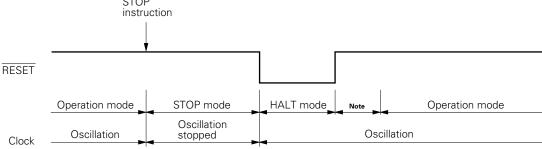

The STOP mode stops the system clock oscillation so that data can be retained at low power voltage. The STOP mode can be entered with the STOP instruction, and can be released by a reset signal (RESET) or high-level input to the P0B1 pin. When the mode is released by a high-level signal input to the P0B1 pin, the program starts with the instruction immediately after the STOP instruction.

When the STOP mode is released forcibly by the reset signal (RESET), normal system reset occurs, and the program starts at address 0H.

#### 7.3 SETTING AND RELEASING THE STANDBY MODES

#### (1) Setting and releasing the HALT mode

Conditions for releasing the HALT mode are selected with the least significant bit of the operand in the HALT instruction as shown in Table 7-1. The high-order three bits of the operand must be set to 0.

#### Table 7-1 Setting/Releasing Conditions Specified in the HALT Instruction

#### HALT $000\underline{X}B \leftarrow 4$ -bit data in the operand

| х | Conditions for setting/releasing the HALT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |